This is a summary and update of what’s known and what’s unknown for all the design kits (DK) that have been tested. As the 0.35u DK was only installed recently, it has not been as extensively tested as the other design kits. However, if the Mentor toolchain is set up properly, the 0.35u DK is more likely to work than the 0.50u/0.70u DK. Our main problem is the incompatibility between toolchain and design kits.

The ideal situation would be to get a copy of the ADK from Mentor. However RJ has not gotten back to me on this. The next best solution is to have the appropriate Mentor software installed but SJM has been unable to do it as yet. According to him, he has been busy trying to fix the security problems and is unable to fix the Mentor problems for now.

HDL Design Entry

- 0.35u – Untested, presumably working as HDL netlist importing is built into DA_IC.

- 0.50u – Tested with ICSTUDIO

- 0.70u – Tested with ICSTUDIO

HDL Behavioral Simulation

- 0.35u – Untested, unknown status

- 0.50u – Tested with MODELSIM. HDL libraries for standard cells are provided.

- 0.70u – Untested, should work like 0.50u as a similar HDL library is provided.

HDL Synthesis

- Untested for ALL as Leonardo Spectrum is unavailable.

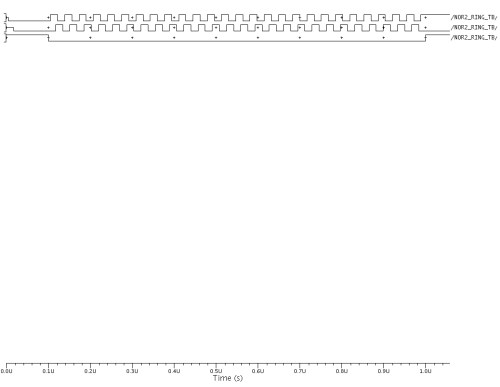

NOR2 Gate Schematic

- 0.35u – Schematic entry works. Simulation is untested.

- 0.50u – Working schematic entry + simulation.

- 0.70u – Working schematic entry + simulation.

NOR2 Layout

- 0.35u – Works automagically.

- 0.50u – NOT working.

- 0.70u – NOT working.

Standard Cell Schematic Capture

- 0.35u – Unknown/Untested.

- 0.50u – Working

- 0.70u – Working

Standard Cell ELDO Simulation (ANASIM)

- 0.35u – Unknown/Untested.

- 0.50u – NOT working.

- 0.70u – Tested and working.

Standard Cell MODELSIM Simulation (DIGISIM)

- 0.35u – Unknown

- 0.50u – Should work (partial testing)

- 0.70u – Should work (similar library provided as 0.50u)

Standard Cell Autofloorplan (AFP)

- Untested for ALL as there seems to be a license problem.

- Will presumable work for 0.35u but may not work with 0.50u/0.70u.

Design Rule Check (DRC)

- 0.35u – Tested and working for the custom NOR2 cell layout

- 0.50u – Untested

- 0.70u – Untested

Layout Versus Schematic (LVS)

- 0.35u – Untested but would likely work.

- 0.50u – Tested and failed

- 0.70u – Untested and presumed NOT to work

Parasitic Extraction (XRC)

- All untested

Back-annotation Simulation (BA)

- Untested for all

on and setup of the Mentor software. Due to the difference in the versions for the AMI05 design kit and the latest Mentor version, the instructions for using the DK are essentially non-applicable. So, I am trying to figure out how to work the DK from within the latest Mentor setup.

on and setup of the Mentor software. Due to the difference in the versions for the AMI05 design kit and the latest Mentor version, the instructions for using the DK are essentially non-applicable. So, I am trying to figure out how to work the DK from within the latest Mentor setup. I’d just gotten back from Malaysia and moved into my new room yesterday. I contacted SJM today and he told me that he’s having problems setting up the Mentor software. However, he thinks that he’ll be able to make some progress soon. I’m not sure what the details of the problems are, but hopefully, they’ll be sorted out soon. He says that the same problems exist for different versions of Mentor software.

I’d just gotten back from Malaysia and moved into my new room yesterday. I contacted SJM today and he told me that he’s having problems setting up the Mentor software. However, he thinks that he’ll be able to make some progress soon. I’m not sure what the details of the problems are, but hopefully, they’ll be sorted out soon. He says that the same problems exist for different versions of Mentor software. I spent some time thinking of a possible new design that might be suitable for the new VLSI project. As the students work in pairs, it would be easiest to get them to design some sort of communications device, with one designing the transmitter and the other the receiver. Then, they can put it all together at the end to see if it works. However, I have to keep in mind that most of these students would have had little exposure to hardware design, much less a VLSI one. This means that the project needs to be suitably easy for noobs, but is also extensible for the experienced few.

I spent some time thinking of a possible new design that might be suitable for the new VLSI project. As the students work in pairs, it would be easiest to get them to design some sort of communications device, with one designing the transmitter and the other the receiver. Then, they can put it all together at the end to see if it works. However, I have to keep in mind that most of these students would have had little exposure to hardware design, much less a VLSI one. This means that the project needs to be suitably easy for noobs, but is also extensible for the experienced few. I’ve just spent a few hours doing a preliminary search of the available design libraries from EUROPRACTICE through the

I’ve just spent a few hours doing a preliminary search of the available design libraries from EUROPRACTICE through the